高速Serdes:半导体产业的前沿发展与投资机遇 | 一村研究社

2023-06-17 19:32:23 来源:财讯网

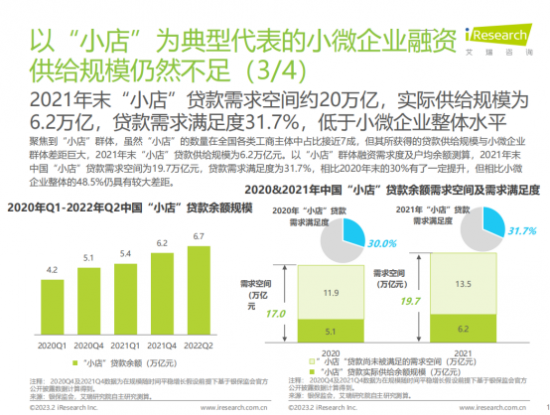

在当前的数字化世界中,半导体已经成为推动科技进步和社会发展的重要驱动力。其中,作为一种关键的高速接口技术,Serdes(Serializer/Deserializer)正在助力实现更高速、更高效的数据传输。特别是在人工智能(AI)领域,这一技术的重要性日益凸显。

在这篇文章中,我们将探讨高速Serdes的概念、应用与市场空间,行业格局,以及国产替代路径,并从中寻找未来的投资机会。

Serdes技术在AI领域的崛起:推动半导体行业迎接高速接口需求

Serdes是一种重要的高速接口技术,主要用于高速数据通信中的串行数据与并行数据间的转换。其核心功能就是将串行数据转换为并行数据,或将并行数据转换为串行数据。除此之外,Serdes是一种时分多路复用(TDM)、点对点的通信技术,即在发送端多路低速并行信号被转换成高速串行信号,经过传输媒体(光缆或铜线),最后在接收端高速串行信号重新转换成低速并行信号。

图片来源:Semiwiki

数据量的增长对更快的服务器接口提出了需求,因为在服务器内部和服务器之间需要搬运大量数据。服务器内的数据移动可能是主要的瓶颈,也是延时的根源。要提高性能,所有内部服务器接口都在进行升级,如NVMe SSD正从PCIe3.0转向PCIe5.0,CXL提供了PCIe电接口上运行的缓存一致性接口,并允许多个处理器共享数据和内存,从而减少系统中需要移动的数据量,而这些接口底层都需要新型高速Serdes技术。

来源:英伟达

在AI领域,随着英伟达等公司AI服务器的推出,高速Serdes的需求越来越大。NVIDIA 在 2016-2022 年迭代 4 代 的NVLink满足了其算力方案的两大需求(专用连接方案解决专业问题),使GPU具有尽可能高的性能、使用专用协议和系统设计以实现更高的性能。

传统的PCIe Gen5每通道仅为32Gbps,而NVLink每通道高达100Gbps、多个通道连接其GPU系统。最新的NVLink 4相比上代从12 Links升级至18 Links, 每个GPU提供900GB/s(7200Gbs)的双向带宽(Bidirectional Bandwidth)。

这些AI服务器对于高速接口的需求日益增加,这也随之推动了对高速PCB和半导体的需求。然而,现行的FR4板材已经无法满足AI服务器对高速Serdes的需求,这一点正在推动整个半导体行业向更高的设计复杂度和制程工艺要求发展。

图片来源:澜起投资

因为SerDes的强电气属性,使得 Serdes具有以下优点:

1. 减少布线冲突(非独立时钟嵌入在数据流中,解决了限制数据传输速率的Signal时钟的Jilter问题);

2. 带宽高;

3. 引脚数目少;

4. 抗噪声、抗干扰能力强(差分传输);

5. 降低开关噪声;

6. 扩展能力强;

7. 更低的功耗和封装成本;

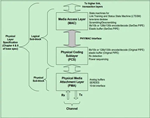

目前高速串行链路数据通信协议都是基于Serdes:Serdes协议的主要作用是把数据实现串并转换,但是PCIe、CXL等协议则是完整的协议,包含物理层、链路层等,其中的物理层PHY就是Serdes协议实现的。PHY本身可以分成:PIPE接口+PCS(物理编码子层)+PMA(Serdes功能)。

来源:互联网

在SerDes收发器内部包括高速串并转换电路、时钟数据恢复电路、数据编解码电路、时钟纠正和通道绑定电路,为各种高速串行数据传输协议提供了物理层(PHY)基础。而主流的8B/10B编码SerDes则主要由物理介质相关子层(PMD)、物理媒介适配层(Physical Media Attachment,PMA)和物理编码子层(Physical Coding Sublayer,PCS)所组成,且收发器的TX发送端和RX接收端功能独立。

高速Serdes技术的挑战与发展方向

随着通信速度的提升,设计敏感度也相应增加,要设计出满足需求的高速Serdes技术存在一定的挑战。一方面,设计复杂度非常高,整个系统涉及的部分包括PMA(Physical Medium Attachment)和PCS(Physical Coding Sublayer),都需要进行数模混合设计,从而导致接收端的设计变得更加复杂。

Serdes是典型的数模混合电路,整个Serdes系统需要一个熟练的模拟/混合信号设计团队来完成。在速度大于56Gbps时,随着PAM-4DSP技术的使用,同样的28ghz带宽信道现在可以支持112gbps的数据速率,但是PAM4信号对噪声、反射、非线性和基线漂移更加敏感,接收器设计要更加复杂。

难点包括高频低抖动时钟的生成(Tx PLL的设计、各种各样的jitter对BER的影响)、信号完整性考虑(如Tx的FFE、Rx的CTLE和DFE)、Rx的CDR实现环路等等;这里面除了模拟电路设计之外,内部还包含了大量数字实现内容:编解码实现、PRBS生成和检查、环回测试、自适应算法实现、系统状态控制数字实现等;

来源:互联网

另一方面,高速Serdes在高频率下运行,对半导体的制程工艺提出了更高的要求。

上一代Serdes往往都是以传统模拟方式实现,从16nm开始,在速度大于56Gbps时,收发器已经转向基于ADC/ DSP的策略,其中有很大一部分仍为模拟电路,但还有接近50%的电路是数字电路。因此,当应用到更加先进节点时,面积和功耗会有一定程度的改善。

当工艺进一步走向高端,工艺加持下后续的架构就是TX:DSP+DAC、RX:ADC+DSP,流片成本会进一步增加,因此目前112G Serdes IP的license市场价就高达数百万美金。

例如,Synopsys公司的112G Serdes是通过5纳米工艺实现的,ISSCC2023 Program中关于Serdes的研究主要关注在112G速度下的功耗优化和均衡能力提升等方面。而要实现超过100G的CDC(Clock and Data Recovery)功能,基本上需要使用至少7纳米的工艺。目前,全球都在致力于突破高速Serdes技术。对于中国来说,发展本土Serdes替代方案是当前的首要任务。

Serdes行业格局与国产替代路径

伴随着Serdes IP技术的快速发展,许多公司已经开始采用这种技术来开发各种创新产品。

•近日,Credo公司发布了基于台积电3纳米工艺的112G长距离Serdes IP。这种技术能够克服线缆损耗,使得连接距离可以比常规的L2技术更长,为高速互联提供了新的可能性。

•Alphawave是目前唯一能够推出7纳米、6纳米、5纳米高速连接功能芯片的公司,他们是当前唯一能够提供传输速度达到224Gbps的纯高速连接IP供应商。

•早在2021年1月,新思科技就已经推出经过硅验证的采用5纳米FinFET工艺的112G以太网PHY IP,提供超出IEEE 802.3ck和OIF标准电气规范的卓越信号完整性和电气性能。另外,用于极短距离接口的新思科技112G以太网PHY可以在大于20dB的信道中以低于3pJ/bit的速度实现出色的BER;用于超短距离接口的新思科技112G以太网PHY可以在大于10dB的信道中以低于1.4pJ/bit实现出色的BER。

•Cadence 在 2023 年 TSMC 北美技术研讨会期间发布了面向台积电 3nm 工艺(N3E)的 112G 超长距离(112G-ELR)SerDes IP 展示。SerDes IP 采用领先的基于 DSP 的架构,通过最大可能性序列检测(MLSD)和反射抵消技术实现损耗及反射信道的系统稳定。MLSD 技术可以优化 BER,提供更强大的突发性错误处理能力。

来源:半导体行业观察

当前,Serdes技术的主要供应商主要集中在北美,这些公司拥有领先的技术和丰富的产品线。对于中国来说,发展本土Serdes技术、实现国产替代变得愈发重要。因为AI不仅涉及算力,还涉及解决高速传输等通信问题的关键技术。因此,中国需要支持具备能力和经验的核心团队,集中资源以实现突破。

技术突破是实现国产替代路径中最大的挑战。目前,国内在高速Serdes领域的研发仍然处于起步阶段,需要克服许多技术难关。但同时,这也为投资者提供了巨大的机会。那些能够成功研发出高性能Serdes产品的企业,有可能抢占巨大的市场份额。

Chris Miller的新作《芯片战》

中国面临的挑战以及高速Serdes技术的投资前景

正如Chris Miller在新作《芯片战》中所表述的那样:芯片已经成为全球地缘政治争夺的最关键的技术之一,影响着全球地缘政治的平衡。

对于中国而言,突破高速接口技术和AI相关的基础芯片开发已成为中美技术竞争的焦点。面对美国对中国半导体领域的禁令,包括AI相关和先进工艺在内的高端领域对国内发展构成重要制约。因此,中国应集中资源,扶持真正有能力和经验的团队来实现技术突破。这不仅是中国半导体产业面临的巨大挑战,同时也是巨大的机遇。

根据预测,全球Serdes市场规模在未来几年内将持续高速增长。根据MarketsandMarkets的报告,预计到2026年,全球Serdes市场规模将达到8亿美元。从国内市场的角度来看,随着对AI服务器以及其他高速设备的需求增加,对高速Serdes的需求也将持续增长。如果国内企业能够成功研发出满足需求的高速Serdes产品,无疑将在市场上获得巨大的机会。对于投资者来说,随着半导体技术的发展和高速数据传输需求的增加,对Serdes技术的需求也将不断增长。

总的来说,高速Serdes无疑是未来半导体技术发展的重要方向。无论是在全球范围内还是在中国市场上,投资者都面临巨大的投资机会。同时,对于那些愿意接受挑战、敢于进行技术创新的企业来说,他们在这个领域有可能取得巨大的成功。

关键词:

相关阅读